Altium + Ansys - Phân tích nhiễu xuyên âm trên giao diện Bus song song FIFO và DDR4

Các bus tốc độ cao, dù là đầu cuối đơn hay vi sai, đều có thể gặp bất kỳ vấn đề nào đó về tính toàn vẹn của tín hiệu. Một vấn đề chính được tạo ra bởi tín hiệu lan truyền là nhiễu xuyên âm, nơi một tín hiệu tự xếp chồng lên một dấu vết gần đó. Đối với các mạng song song, điều này đặc biệt có vấn đề vì nó dẫn đến hỏng dữ liệu trong những trường hợp nghiêm trọng. Mặc dù bạn có thể làm chậm thời gian tăng của tín hiệu, nhưng điều này có thể yêu cầu giảm tốc độ truyền dữ liệu và có thể không được chấp nhận trong một số ứng dụng.

Nếu bạn muốn xác định nhiễu xuyên âm trên bus song song, nó có thể khá khó khăn khi bus khá rộng. Đối với bus song song N -bit, bạn sẽ cần chạy mô phỏng nhiễu xuyên âm N ( N - 1) để kiểm tra nhiễu xuyên âm giữa mọi kết hợp có thể có của dấu vết của lỗi và nguyên nhân gây lỗi. Khi bạn đạt đến độ rộng bus, điều này sẽ trở nên rất tốn thời gian nếu không có bộ công cụ phân tích phù hợp. Thông thường, bạn chỉ cần trích xuất tín hiệu xuyên âm đỉnh và so sánh nó với thông số kỹ thuật tín hiệu của bạn.

Các công cụ thiết kế PCB tiêu chuẩn công nghiệp trong Altium Designer®

đã bao gồm một trình mô phỏng sau bố cục để kiểm tra nhiễu xuyên âm . Tuy nhiên, bạn có thể tăng tốc độ phân tích xuyên âm trong các bus song song khi bạn sử dụng một bộ giải trường mạnh mẽ. Bạn có thể tiến hành phân tích nhiễu xuyên âm trên các bus song song và các nhóm tín hiệu khác khi nhập bố cục Altium Designer

của mình vào Ansys SIwave® . Khi bạn có thể dễ dàng hình dung nhiễu xuyên âm giữa các lưới trong một giao diện song song-nối tiếp rộng, bạn có thể tăng tốc độ phân tích và nhanh chóng sửa lỗi trong bố cục PCB của mình.

Điều gì tạo nên tính toàn vẹn của tín hiệu trên các mạng song song?

Trong việc Xác định EMI trường gần trong mạng phân phối điện của PCB và phát hiện các vi phạm trở kháng DDR4 trong thiết kế PCB tốc độ cao, chúng tôi đã xem xét dự án ví dụ về PC mini trong Altium Designer

và chúng tôi đã kiểm tra EMI trường gần do thiết kế không chuẩn. đường dẫn trở lại và các biến thể trở kháng trên mạng DDR4. Vì các lưới DDR4 tạo thành một bus song song (chứa cả tín hiệu vi sai và tín hiệu một đầu), nên cũng có khả năng xảy ra nhiễu xuyên âm trên các mạng này. Một bus song song rộng khác có khả năng giao tiếp chéo giữa các lớp cụ thể là bus rộng 32 bit được định tuyến tới giao diện FIFO-to-USB.

Khi các nhóm lưới song song này tạo thành các bus rộng, việc phân tích nhiễu xuyên âm trên mọi tín hiệu và trích xuất điện áp nhiễu xuyên âm từ đỉnh đến đỉnh có thể rất tốn thời gian.

Thay vào đó, nhiễu xuyên âm trên các mạng này có thể được trích xuất trực tiếp bằng cách sử dụng bộ giải trường trong Máy quét xuyên âm trong Ansys SIwave. Sau khi hoàn thành bố cục của bạn trong Altium Designer

, phần mở rộng Ansys EDB Exporter có thể được sử dụng để chuyển thiết kế sang SIwave và chạy mô phỏng trực tiếp từ dữ liệu bố cục PCB. Một số chỉ số tính toàn vẹn tín hiệu quan trọng khác có thể được kiểm tra bao gồm:

-

Sự thay đổi trở kháng trên các lưới một đầu và các lưới khác nhau

-

Đường dẫn trả về cho tín hiệu tốc độ cao

-

Trích xuất thông số S, Y và Z trên các lưới quan trọng

-

Khai thác ký sinh trên lưới quan trọng

Trong ví dụ này, chúng ta sẽ bắt đầu bằng cách xem xét nhiễu xuyên âm một đầu trên mạng FIFO, tiếp theo là mạng DDR4. Như chúng ta sẽ thấy sớm, Ansys SIwave cung cấp một hình ảnh trực quan thuận tiện cho phép xác định cặp mạng nạn nhân / kẻ xâm lược. Một giải pháp tiềm năng cho cặp lưới có thể được thực hiện và mạng đã sửa đổi có thể được phân tích chi tiết hơn bằng cách sử dụng các công cụ mô phỏng sau bố cục trong Altium Designer.

FIFO - to - USB Nets

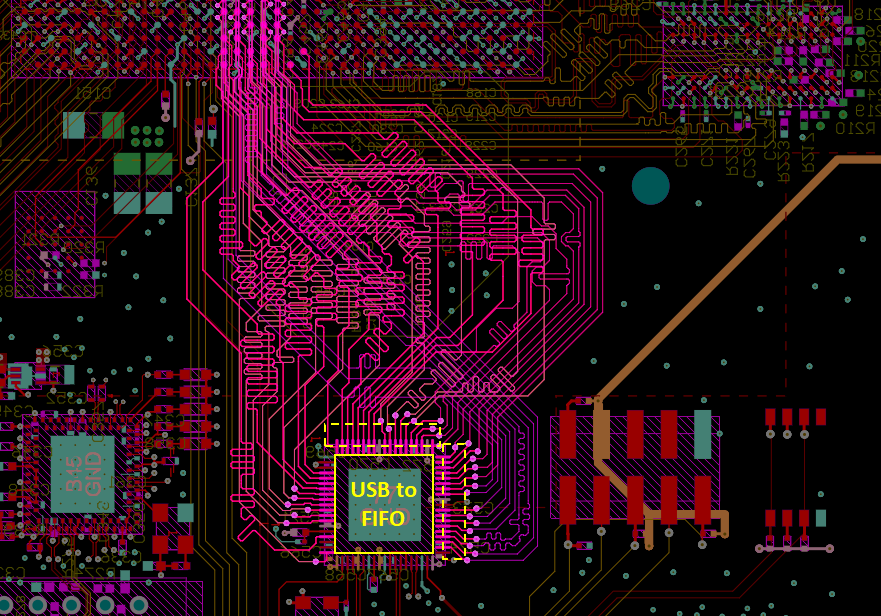

Hình 1 cho thấy các lưới FIFO được đánh dấu trên các Lớp 1, 5 và 7. Các lưới này tạo thành một bus song song rộng 32 bit với xung nhịp đồng bộ nguồn một đầu kết nối với IC giao diện FIFO-to-USB (U33 trong Mini Dự án PC). Đối sánh độ dài đã được thực thi để ngăn chặn sự lệch giữa đồng hồ đồng bộ và các đường dữ liệu 32 bit trong xe buýt này. Các lưới trong các lớp này được ngăn cách bởi các mặt phẳng lớn trên các lớp xen kẽ.

Hình 1: Các lưới FIFO được kết nối với giao diện FIFO-to-USB (U33) trong bố cục Mini PC. Các đường đứt nét hiển thị các kết nối được thực hiện với bus FIFO song song 32 bit.

Bộ nhớ DDR4

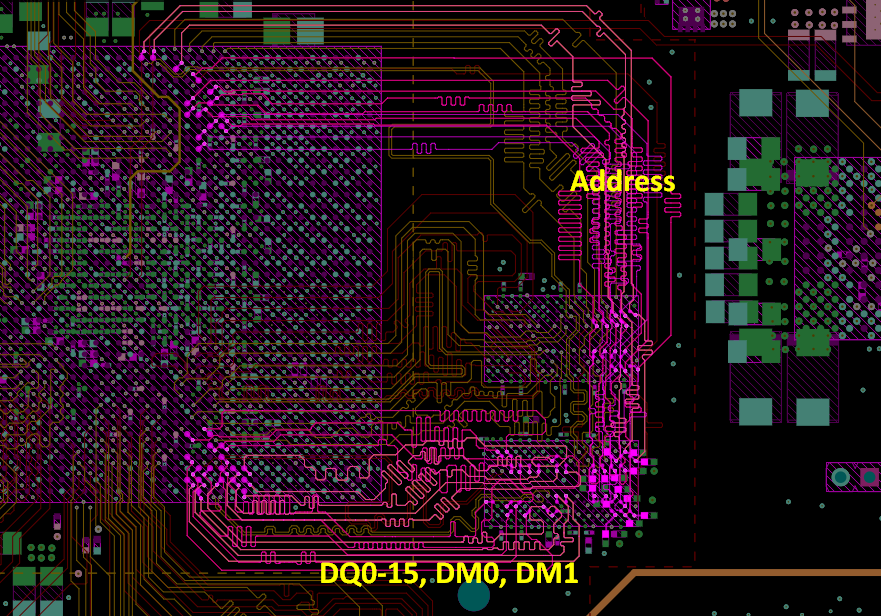

Bo mạch Mini PC chứa hai chip DDR4 DRAM 8 GB trên bo mạch chạy ở tốc độ 1866 MHz được định tuyến theo cấu trúc liên kết nhanh. Các làn byte 0 và 1 được nhóm lại với nhau với khả năng định tuyến chặt chẽ và khớp độ dài trong một khu vực của bo mạch, trong khi các đường địa chỉ được định tuyến xung quanh mép của các mô-đun DDR4 theo cấu trúc liên kết di chuyển điển hình. Ở đây, về cơ bản chúng ta có hai bus song song để mô phỏng: đường địa chỉ và đường DQ / DM dẫn đến mỗi mô-đun. Hình 2 cho thấy các đường địa chỉ, DQ và DM sẽ được kiểm tra trong cách bố trí Mini PC

Hình 2: Các mạng DDR4 một đầu nổi bật được định tuyến đến mô-đun DRAM (U15) trong bố cục Mini PC.

Kết quả máy quét xuyên âm.

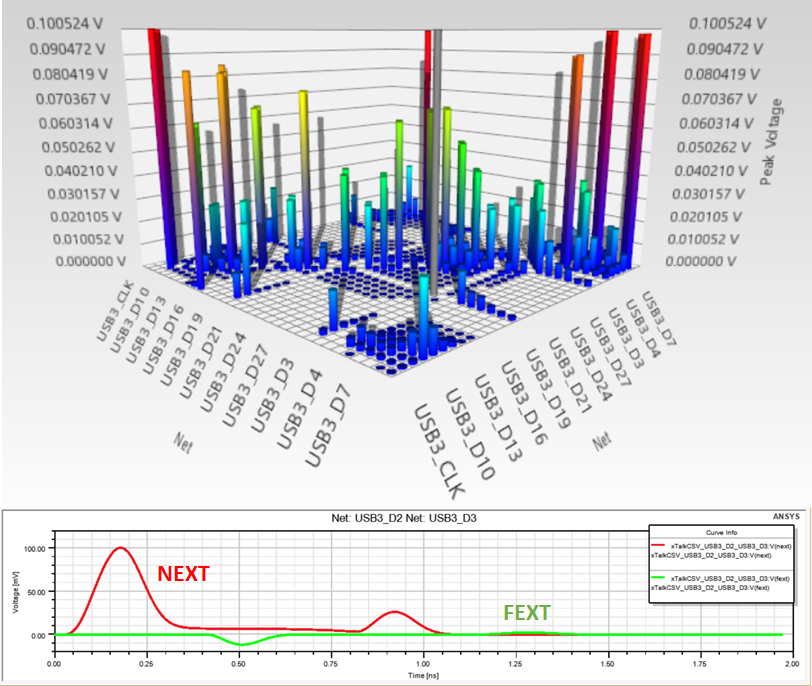

Sau khi chạy Trình quét xuyên âm trong SIwave cho các xe buýt song song được hiển thị ở trên, chúng ta có thể thấy chính xác cặp mạng nào có tín hiệu xuyên âm lớn nhất (NEXT và FEXT). Công cụ này sử dụng một tín hiệu kích thích lý tưởng phù hợp với thời gian tăng / giảm của FPGA trong bảng này. Điện áp đỉnh-đỉnh có thể được hiển thị trong biểu đồ thanh 3D, trong đó tên ròng được đặt trên trục x và y để tạo thành ma trận vuông đối xứng. Các tín hiệu xuyên âm FEXT và NEXT được tạo ra bởi một cặp mạng nhất định cũng có thể được hiển thị trong miền thời gian.

Hình 3 cho thấy nhiễu xuyên âm từ đỉnh đến đỉnh (NEXT) cho các lưới FIFO được thể hiện trong Hình 1; chỉ một tập hợp con của các lưới FIFO dẫn đến IC FIFO đến USB được hiển thị rõ ràng. Điện áp đỉnh-đỉnh đối với tín hiệu xuyên âm gây ra khá lớn và đạt 100 mV hoặc 8,33% mức tín hiệu một đầu danh định (1,2 V) trên các lưới này. Điều này cho thấy sự cô lập tương đối thấp, đặc biệt là giữa tín hiệu đồng hồ (USB3_CLK) và một số mạng dữ liệu lân cận (NEXT mạnh nhất được thấy là USB3_D10).

Phần dưới cùng của Hình 3 cho thấy tín hiệu xuyên âm được trích xuất từ USB3_D2 đến USB3_D3 trong miền thời gian. Ở đây, chúng ta thấy rằng tín hiệu FEXT khá thấp và chỉ đạt ~ 10 mV (-21 dB). Ngược lại, NEXT tương đối cao và đạt ~ 100 mV.

Hình 3: Xuyên âm (NEXT) cho lưới FIFO trong bố cục Mini PC.

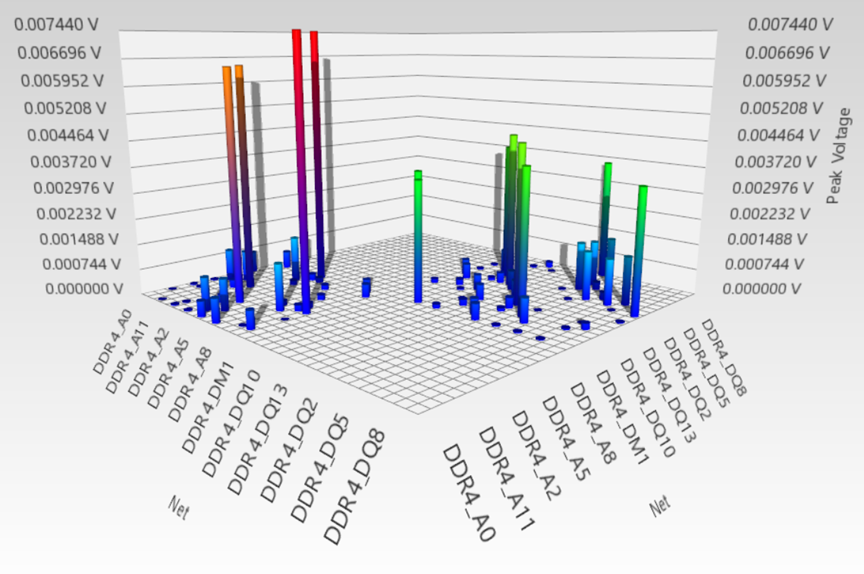

Hình 4 cho thấy nhiễu xuyên âm từ đỉnh đến đỉnh (NEXT) cho các lưới DDR4 được thể hiện trong Hình 2; chỉ một tập hợp con của các lưới trong Hình 2 được hiển thị cho rõ ràng. Điện áp đỉnh-đỉnh cho tín hiệu xuyên âm gây ra không vượt quá 7,5 mV, hoặc 0,625% mức tín hiệu chế độ chung danh định trên các lưới một đầu này. Điều này tương đương với cách ly tối thiểu -22 dB giữa các lưới địa chỉ, đủ cho các hệ thống bộ nhớ hiệu suất cao. Các lưới khác trong phần DQ / DM có độ cách ly cao hơn nhiều. Cuối cùng, các phần địa chỉ và DQ / DM được phân tách rõ ràng bằng đủ không gian để nhiễu xuyên âm không có vấn đề.

Hình 4: TIẾP THEO cho một số mạng DDR4 một đầu được chuyển đến mô-đun DRAM (U15) trong bố cục Mini PC.

Vì bo mạch Mini PC là một hệ thống bất biến thời gian tuyến tính (LTI) và trường điện từ không truyền qua bất kỳ phương tiện phi tuyến phân cực nào, nên một cách hợp lý sẽ mong đợi hệ thống tương hỗ, tức là, tín hiệu xuyên âm sẽ giống nhau nếu nạn nhân và lưới xâm lược được hoán đổi. Điều này thực sự có thể được nhìn thấy trong kết quả xuyên âm đối với mạng FIFO và mạng DDR4. Vì bus DDR4 nằm trong giới hạn nhiễu xuyên âm được tìm thấy trong các hệ thống bộ nhớ hiệu suất cao, chúng ta có thể tập trung vào các sửa đổi tiềm năng đối với bus FIFO.

Giảm nhiễu xuyên âm trên bus FIFO

Khi kiểm tra bố cục FIFO và kết quả NEXT, rõ ràng nhiễu xuyên âm quy nạp chiếm ưu thế trong các dấu vết trong bus này. Do đó, giải pháp tự nhiên, trong trường hợp này, là giảm độ tự cảm của những vết này bằng cách làm cho chúng rộng hơn hoặc bằng cách đưa chúng đến gần mặt phẳng tham chiếu của chúng hơn.

Mặc dù thay đổi ngăn xếp là không đủ, nhưng vẫn có đủ chỗ trên Lớp 1, 5 và 7 để mở rộng dấu vết. Khoảng cách giữa các vết nên được duy trì để ngăn ngừa sự gia tăng điện dung lẫn nhau khi các vết này lan rộng ra. Nếu chúng ta nhìn vào Hình 1, bus FIFO nên được trải rộng về phía bên phải của hình ảnh. Đối sánh độ dài sẽ cần được thực thi vì các sửa đổi được áp dụng cho các dấu vết trong bus FIFO.

Tóm lược

Nhiễu xuyên âm trên giao diện bus song song Dự án ví dụ về máy tính mini của Altium Designer đã được kiểm tra bằng cách sử dụng Máy quét xuyên âm trong Ansys SIwave. Các mạng cụ thể trong các bus FIFO và DDR4 đã được xác định để sửa đổi bằng cách sử dụng hình ảnh xuyên âm thuận tiện, tóm tắt các tín hiệu nhiễu xuyên âm gây ra cho các cặp lưới xâm lược và nạn nhân. Hơn nữa, cơ chế xuyên âm chiếm ưu thế (cảm ứng so với điện dung) có thể được xác định từ việc xem xét các dạng sóng miền thời gian, sau đó giúp xác định một số giải pháp để triển khai trong Altium Designer.

Bằng cách sử dụng tiện ích mở rộng Ansys EDB Exporter trong Altium Designer® , các nhà thiết kế PCB có thể chuyển bố cục PCB của họ sang Ansys SIwave® và chạy nhiều mô phỏng toàn vẹn tín hiệu và toàn vẹn nguồn. Gói mô phỏng này lấy dữ liệu trực tiếp từ bố cục PCB của bạn và cung cấp cho các nhà thiết kế quyền truy cập vào nhiều bộ giải trường 3D cho các mô phỏng và phân tích miền thời gian hoặc miền tần số.